#### International Journal of Emerging Trends in Computer Science and Information Technology

ISSN: 3050-9246 | https://doi.org/10.63282/30509246/IJETCSIT-V5I1P102 Eureka Vision Publication | Volume 5, Issue 1, 11-20, 2024

Original Article

# High-Performance Computing Architectures: Memory Hierarchy Optimization Strategies

Dr. Narmada School of Computing, Goa University, Goa.

Abstract - Memory hierarchy is a critical component in high-performance computing (HPC) architectures, influencing the efficiency and speed of data processing. This paper explores various optimization strategies aimed at enhancing memory hierarchy performance. The memory hierarchy is structured to minimize access time and maximize throughput by organizing different types of memory based on speed, capacity, and cost. Key strategies include the implementation of advanced caching techniques, such as behavior-aware cache hierarchies that dynamically allocate resources based on runtime demands, and the use of partial breadth-first search algorithms to optimize memory consumption during data processing tasks. Additionally, the integration of high-bandwidth memory (HBM) and non-volatile memory technologies presents opportunities for further performance improvements. By analyzing the trade-offs between latency and bandwidth, this research provides insights into designing memory systems that effectively support the increasing computational demands of modern applications. The findings underscore the importance of optimizing memory architecture to achieve significant enhancements in overall system performance, particularly in data-intensive environments.

Keywords - Memory hierarchy, high-performance computing, optimization strategies, caching techniques, data throughput, latency, bandwidth, behavior-aware cache, high-bandwidth memory.

#### 1. Introduction

High-performance computing (HPC) has become a cornerstone of modern scientific research, engineering simulations, and data-intensive applications. As the demand for computational power continues to grow, optimizing the underlying architecture, particularly the memory hierarchy, is essential for achieving peak performance. The memory hierarchy plays a pivotal role in determining how efficiently data is accessed and processed by the CPU, directly impacting the overall speed and efficiency of computations.

#### 1.1. Importance of Memory Hierarchy in HPC

The memory hierarchy in HPC systems typically consists of multiple layers, including registers, caches, main memory (RAM), and secondary storage. Each layer is designed with specific trade-offs between speed, capacity, and cost. Registers are the fastest but have limited capacity, while secondary storage offers vast amounts of space at the expense of speed. This hierarchical structure aims to bridge the gap between the CPU's processing speed and the slower access times associated with larger memory units. Effective management of this hierarchy is crucial for minimizing latency and maximizing data throughput.

#### 1.2. Challenges in Memory Management

Despite advancements in hardware design, several challenges persist in memory management within HPC architectures. One significant issue is the increasing disparity between CPU speeds and memory access times, often referred to as the memory wall. As processors become faster, the time taken to retrieve data from memory can become a bottleneck in performance. Additionally, data locality where frequently accessed data is stored close to the processing unit can be difficult to achieve in complex applications with dynamic data access patterns. Moreover, as applications scale up in complexity and size, traditional caching strategies may not suffice. The need for adaptive techniques that can respond to varying workloads and access patterns is more pressing than ever. This necessitates innovative strategies that enhance cache efficiency and reduce memory access latencies.

#### 1.3. Overview of Optimization Strategies

To address these challenges, this paper will explore various optimization strategies for memory hierarchy in HPC systems. These include advanced caching techniques that adapt to runtime conditions, leveraging high-bandwidth memory technologies, and employing algorithms designed to optimize memory usage during data processing tasks. By focusing on these strategies, we aim to provide insights into developing more efficient memory architectures that can keep pace with the growing demands of high-performance computing applications.

#### 2. Memory Hierarchy in High-Performance Computing

Hierarchical model of memory in computing architectures, illustrating the different levels of storage available in a computer system. It is structured to show the relationship between registers, cache, main memory (RAM), and secondary storage, emphasizing their relative speeds, access times, and roles in computation.

At the top of the hierarchy, registers are the fastest and smallest form of memory, located directly within the CPU. These store frequently accessed instructions and data for immediate processing. Below the registers, cache memory (L1, L2, and L3) is slightly larger and serves as a high-speed buffer between the CPU and main memory, reducing the latency of data retrieval.

#### small size processor registers small capacity very fast, very expensive power on immediate term small size processor cache small capacity very fast, very expensive medium size power on random access memory very short term fast, affordable medium capacity small size power off flash / USB memory large capacity short term slower, cheap hard drives power off large size very large capacity mid term slow, very cheap power off large size tape backup very slow, affordable very large capacity long term

## Computer Memory Hierarchy

Figure 1. Memory Hierarchy Model in High-Performance Computing

Further down, the main memory (RAM) acts as the primary volatile storage, holding data and instructions required by active processes. It is significantly larger than the cache but operates at lower speeds. Since RAM is limited in capacity and cannot retain data after power loss, secondary storage plays a crucial role in long-term data retention. At the base of the hierarchy, secondary storage devices such as solid-state drives (SSD) and hard disk drives (HDD) provide massive storage capacity but have significantly slower access speeds. This level also includes virtual memory, which extends RAM using disk storage to manage workloads that exceed available physical memory. This image effectively demonstrates the trade-offs between speed, cost, and capacity in memory design. High-performance computing architectures optimize this hierarchy to balance computational efficiency with energy and cost constraints. Proper understanding of these memory layers enables the development of optimization strategies such as caching techniques, memory prefetching, and efficient data locality management to enhance overall system performance.

#### 3. Optimization Strategies for Memory Hierarchy

### 3.1. Cache Optimization Techniques

3.1.1. Cache Organization and Policies (L1, L2, L3)

Cache memory is structured in a multi-level hierarchy to optimize data access speeds and efficiency. The levels typically include L1, L2, and L3 caches, each with distinct characteristics and roles in the memory hierarchy.

- L1 Cache: This is the smallest and fastest cache, located closest to the CPU cores. It typically has a size ranging from 16KB to 64KB and is divided into separate instruction and data caches (Harvard architecture). The primary function of the L1 cache is to provide rapid access to frequently used data and instructions, minimizing latency. The hit time for L1 cache is significantly lower than that of L2 or L3 caches, making it crucial for performance.

- L2 Cache: Larger than L1, the L2 cache usually ranges from 256KB to several megabytes. It serves as a secondary cache that holds data that does not fit in L1 but is still accessed frequently. The L2 cache can be either dedicated per core or shared among multiple cores, depending on the architecture. While it has a longer access time compared to L1, it still provides faster access than main memory.

• L3 Cache: The largest of the three, L3 cache sizes can reach several megabytes (up to 30MB or more). It is typically shared among all cores in a processor and serves as a last line of defense before accessing the slower main memory. Although it has higher latency than both L1 and L2 caches, its larger size allows it to store more data, reducing the overall miss rate across the processor.

Cache policies such as replacement strategies (e.g., Least Recently Used (LRU), First In First Out (FIFO)) and mapping techniques (direct-mapped, set-associative) are vital for maintaining optimal performance across these levels by determining how data is stored and replaced within the caches.

#### 3.1.2. Cache Blocking and Tiling Strategies

Cache blocking (or tiling) is an optimization technique used to enhance data locality by reorganizing data access patterns in memory-intensive applications. This strategy involves dividing large datasets into smaller blocks or tiles that fit within cache memory limits. By ensuring that operations on these blocks are performed before moving on to others, cache blocking minimizes cache misses and maximizes cache utilization. In practice, when processing multi-dimensional arrays (common in scientific computing), algorithms are restructured so that computations are performed on smaller sub-arrays or tiles that can be fully loaded into the cache. This approach reduces the frequency of accessing slower main memory by keeping relevant data close to the CPU. For example, in matrix multiplication algorithms, instead of iterating through entire matrices, developers can iterate over smaller blocks of matrices. This reduces the number of cache misses significantly as the working set of data fits into the faster cache layers. The benefits of cache blocking include improved performance due to reduced memory latency and increased throughput as more operations can be performed with cached data. However, implementing this strategy requires careful consideration of block sizes relative to cache sizes and application characteristics.

#### 3.1.3. Prefetching Techniques

Prefetching is an advanced technique aimed at mitigating latency by preloading data into the cache before it is actually needed by the CPU. This proactive approach helps reduce wait times associated with memory accesses. There are two primary types of prefetching: hardware prefetching and software prefetching.

- Hardware Prefetching: This method relies on built-in mechanisms within the CPU or memory controller to predict which data will be needed next based on historical access patterns. Hardware prefetchers analyze past memory accesses and automatically fetch likely future requests into the cache. Techniques such as stride-based prefetching detect regular patterns in data access (e.g., sequential array accesses) and preload subsequent blocks accordingly.

- **Software Prefetching**: This technique involves explicit instructions added by programmers or compilers into code to load data into caches ahead of time. Software prefetching can be particularly effective when developers have knowledge about access patterns that hardware cannot predict effectively.

Effective prefetching can significantly reduce miss penalties associated with cache misses by ensuring that required data is available in the cache when needed. However, it also poses challenges such as increased bandwidth consumption and potential pollution of cache lines with unnecessary data if predictions are incorrect.

#### 3.2. Memory Access Optimization

#### 3.2.1. Data Locality and Access Patterns

Data locality is a fundamental principle in optimizing memory access in high-performance computing (HPC). It refers to the tendency of a processor to access a relatively small and localized set of data repeatedly over a short period. This phenomenon can be categorized into two types: temporal locality, where recently accessed data is likely to be accessed again soon, and spatial locality, where data located close to recently accessed data is likely to be accessed next. To leverage data locality, programmers must design algorithms and data structures that enhance cache utilization. For instance, accessing elements of arrays in a sequential manner (row-major order for C/C++ or column-major order for Fortran) ensures that consecutive memory addresses are accessed, maximizing cache hits. This approach minimizes the number of cache misses, which can significantly degrade performance due to the higher latency associated with fetching data from main memory.

Moreover, understanding access patterns is crucial for optimizing data locality. Applications that exhibit predictable access patterns can benefit from tailored optimizations. For example, in matrix operations, algorithms can be structured to process smaller blocks or tiles of matrices that fit within the cache, thereby increasing the likelihood that required data remains in cache during computation. In contrast, irregular access patterns, common in graph algorithms or certain scientific computations, require more sophisticated techniques such as locality-aware scheduling and load balancing to improve performance.

#### 3.2.2. Software-Managed Memory Optimizations

Software-managed memory optimizations involve techniques that allow programmers to control memory allocation and access explicitly, thereby enhancing performance in HPC systems. These optimizations are particularly relevant in environments where hardware management is insufficient or where specific application needs dictate a more tailored approach. One common

technique is memory pooling, where a large block of memory is allocated upfront and then subdivided into smaller chunks for use by various components of an application. This reduces the overhead associated with frequent memory allocation and deallocation, which can lead to fragmentation and performance degradation. By managing memory pools effectively, applications can achieve better performance through reduced allocation times and improved cache utilization.

Another critical aspect of software-managed memory optimization is manual prefetching. While hardware prefetchers can predict some access patterns, they may not always be effective for all workloads. By explicitly inserting prefetch instructions into code, developers can ensure that critical data is loaded into cache before it is needed by the CPU. This technique requires a deep understanding of the application's access patterns but can lead to substantial performance gains if implemented correctly. Additionally, optimizing data structures for alignment can enhance performance by ensuring that data accesses align with cache line boundaries. Misaligned data accesses can lead to additional cycles spent fetching data from memory. Using aligned data structures allows for more efficient use of cache lines and reduces latency.

#### 3.2.3. Memory Alignment and Stride Optimization

Memory alignment and stride optimization are crucial techniques for enhancing memory access efficiency in HPC applications. Memory alignment refers to arranging data in memory so that it adheres to specific boundaries (e.g., 4-byte or 8-byte boundaries). Properly aligned data accesses are faster because they minimize the number of cache lines accessed when reading or writing data. When data is misaligned, accessing it may require multiple read operations from different cache lines, leading to increased latency and reduced throughput. For example, if an array of integers is not aligned properly, accessing an integer at an odd address may require fetching two separate cache lines instead of one. Thus, ensuring that arrays and structures are aligned according to their size can significantly improve performance.

Stride optimization focuses on how data is accessed within arrays or matrices. A stride refers to the number of elements skipped between consecutive accesses in a loop. Accessing elements with a unit stride (i.e., accessing every element sequentially) maximizes spatial locality and ensures that fetched data remains in the cache longer. Conversely, accessing elements with a large stride can lead to poor cache utilization as it may result in many cache misses. Optimizing stride involves restructuring loops or algorithms to minimize strides when accessing multi-dimensional arrays. For instance, when processing matrix rows stored in contiguous memory locations (row-major order), iterating through rows sequentially rather than columns will enhance performance due to better cache utilization.

#### 3.3. Bandwidth and Latency Reduction

#### 3.3.1. Efficient Use of DRAM and NUMA Architectures

Dynamic Random Access Memory (DRAM) is a critical component in high-performance computing (HPC) systems, providing the necessary speed and capacity for data-intensive applications. However, optimizing its use is essential for minimizing latency and maximizing bandwidth. One effective strategy is to leverage Non-Uniform Memory Access (NUMA) architectures, which allow processors to access local memory faster than remote memory. In a NUMA architecture, memory is divided among multiple nodes, each with its own local memory. This design significantly reduces latency for processes that access their local memory, as opposed to accessing memory located on a different node. To optimize performance, applications should be designed to allocate memory close to the processing units that will use it. This can be achieved through thread affinity settings that bind threads to specific CPUs and their associated local memory.

Furthermore, employing memory interleaving techniques can enhance bandwidth utilization across different nodes. By distributing data evenly across multiple memory banks, interleaving allows simultaneous access to different banks, effectively increasing the available bandwidth. This strategy is particularly beneficial in workloads characterized by high data throughput requirements, such as scientific simulations and large-scale data analytics. Another optimization involves using memory access patterns that minimize remote memory accesses. For example, data structures should be organized in a way that keeps frequently accessed data together and close to the processing unit. This approach not only reduces latency but also enhances cache performance by ensuring that relevant data is likely to reside in the cache when needed.

#### 3.3.2. Data Compression Techniques

Data compression techniques play a vital role in reducing the amount of data that needs to be transferred across networks or stored in memory, thereby improving bandwidth utilization and reducing latency. In high-performance computing environments, where large datasets are common, applying effective compression algorithms can lead to substantial performance gains.

There are two primary types of data compression: lossless and lossy compression. Lossless compression algorithms, such as ZIP or LZ77, allow for the original data to be perfectly reconstructed from the compressed data. This type of compression is essential for applications where data integrity is critical, such as scientific simulations or financial calculations. By reducing the size of datasets without any loss of information, these algorithms decrease the time required for data transfer and storage. On the

other hand, lossy compression techniques sacrifice some degree of fidelity for greater reductions in size. These methods are often used in multimedia applications where slight inaccuracies are acceptable. For instance, JPEG compression for images or MP3 compression for audio files can significantly reduce file sizes while maintaining acceptable quality levels. In HPC contexts, specialized libraries such as ZFP or Blosc are designed for compressing numerical arrays efficiently without compromising performance. These libraries utilize tailored algorithms that exploit the characteristics of numerical data to achieve high compression ratios while allowing fast decompression speeds.

Moreover, integrating compression techniques directly into data transfer protocols can further enhance performance by minimizing the volume of data transmitted over the network. For example, using compressed formats during communication between nodes in an HPC cluster reduces both bandwidth consumption and transmission time.

#### 3.3.3. Interconnect and Memory Bus Optimizations

Interconnects and memory buses are crucial components of high-performance computing architectures that determine how efficiently data moves between processors and memory subsystems. Optimizing these pathways is essential for reducing latency and maximizing bandwidth. One effective strategy is to utilize high-speed interconnect technologies such as InfiniBand or RDMA (Remote Direct Memory Access). These technologies allow for low-latency communication between nodes by enabling direct access to remote memory without involving the CPU for every transaction. This capability significantly reduces overhead and improves overall system throughput. Additionally, optimizing the topology of interconnect networks can lead to enhanced performance. For instance, employing a fat-tree topology allows for multiple paths between nodes, which helps balance traffic loads and minimize bottlenecks during peak usage times. Such designs ensure that no single link becomes overwhelmed with traffic, thereby maintaining low-latency communication across the network. Memory bus optimizations also play a critical role in enhancing performance. Techniques such as increasing bus width or frequency can lead to higher data transfer rates between memory modules and processors. Furthermore, implementing dual-channel or quad-channel configurations allows for simultaneous transfers across multiple channels, effectively doubling or quadrupling the available bandwidth. Another important aspect is managing contention on shared buses effectively. Using Quality of Service (QoS) mechanisms can prioritize critical tasks over less important ones during high-demand periods. By ensuring that time-sensitive operations receive preferential treatment on shared resources, overall system responsiveness can be improved.

#### 3.4. Emerging Technologies for Memory Optimization

#### 3.4.1. Non-Volatile Memory (NVM)

Non-volatile memory (NVM) represents a transformative shift in memory technology, offering the ability to retain data even when power is lost. This characteristic makes NVM particularly attractive for high-performance computing (HPC) applications, where data persistence and reliability are paramount. Emerging NVM technologies, such as Phase-Change Memory (PCM), Memristors, and Spin-Transfer Torque RAM (STT-RAM), promise significant advantages over traditional DRAM, including higher density and reduced refresh power requirements. One of the primary benefits of NVM is its potential for inmemory checkpointing, which allows applications to save their state without incurring the overhead associated with traditional disk-based storage. This capability can significantly improve fault tolerance in HPC environments, enabling faster recovery from hardware failures. For instance, frameworks like EasyCrash utilize NVM to maintain application state across crashes, improving system efficiency by up to 30% through selective data persistence strategies.

However, the integration of NVM into existing architectures poses challenges. While NVM offers comparable read latencies to DRAM, its write latencies can be significantly higher, which may impact performance in write-intensive applications. Research indicates that optimizing parameters such as write cancellation techniques and internal caching can mitigate some of these latency issues. Furthermore, the design of hybrid memory systems that combine DRAM with NVM can leverage the strengths of both technologies, providing a balance between speed and persistence. As NVM technologies mature, their adoption in HPC systems is expected to grow. The development of efficient management techniques and architectures will be crucial for maximizing the benefits of NVM while addressing its limitations. Overall, NVM stands to revolutionize memory optimization strategies within HPC by enhancing data resilience and operational efficiency.

#### 3.4.2. High-Bandwidth Memory (HBM)

High-bandwidth memory (HBM) is an innovative memory technology designed to overcome the limitations of traditional memory architectures by providing significantly higher bandwidth and lower power consumption. HBM achieves this by stacking multiple memory chips vertically and connecting them through a high-speed interface called the High Bandwidth Memory Interface (HBM2). This architecture allows for greater data transfer rates compared to conventional DDR memory. The primary advantage of HBM lies in its ability to provide substantial bandwidth—often exceeding 1 TB/s—making it ideal for data-intensive applications such as machine learning, graphics processing, and scientific simulations. The increased bandwidth reduces the time required for data transfers between the CPU and memory, addressing one of the critical bottlenecks in high-performance computing systems.

Moreover, HBM's compact design not only saves space on circuit boards but also reduces power consumption due to shorter signal paths and lower operating voltages. This efficiency is particularly beneficial in environments where thermal management is crucial, such as data centers or mobile devices. However, integrating HBM into existing architectures requires careful consideration of compatibility with current systems and workloads. Applications must be optimized to take full advantage of HBM's capabilities; otherwise, performance gains may not be realized. Additionally, the cost of HBM remains higher than traditional DRAM solutions, which can limit its widespread adoption. As research continues into optimizing HBM usage within HPC environments, it is expected that future advancements will further enhance its performance characteristics. The combination of increased bandwidth and energy efficiency positions HBM as a leading candidate for next-generation memory solutions in high-performance computing applications.

#### 3.4.3. Processing-in-Memory (PIM)

Processing-in-memory (PIM) is an emerging paradigm that integrates computational capabilities directly into memory chips, effectively reducing data movement between the CPU and memory. This approach addresses one of the most significant bottlenecks in modern computing architectures: the latency associated with transferring large volumes of data back and forth between processing units and memory. PIM leverages the inherent parallelism of memory operations by allowing computations to occur where the data resides. This capability is particularly beneficial for workloads characterized by large datasets and repetitive calculations—common in fields such as machine learning and big data analytics. By performing operations like filtering or aggregation directly within the memory array, PIM can drastically reduce latency and increase throughput.

Several architectural designs have been proposed to implement PIM effectively. For instance, some designs utilize specialized logic gates embedded within DRAM cells or employ new types of non-volatile memories that support processing capabilities. These innovations aim to maintain compatibility with existing software ecosystems while enhancing performance. Despite its potential advantages, PIM also faces challenges related to programmability and integration into current computing frameworks. Developing efficient programming models that can exploit PIM's capabilities will be essential for widespread adoption. Additionally, ensuring that PIM architectures can coexist with traditional processing units without significant overhead will be crucial for transitioning from conventional systems.

#### 4. Performance Evaluation and Benchmarking

Benchmarking methodologies play a crucial role in evaluating memory system performance in high-performance computing (HPC) environments. These methodologies help identify bottlenecks, assess optimization strategies, and guide future improvements. A comprehensive approach involves selecting appropriate benchmarks, defining performance metrics, and establishing controlled testing environments to ensure accurate assessments. Choosing the right benchmarks is essential for meaningful performance evaluation. Traditional benchmarks like LINPACK and STREAM focus on specific performance aspects, such as floating-point operations or memory bandwidth. While STREAM provides insights into memory access patterns, it may not fully capture real-world application complexities. To address this, comprehensive suites like the HPC Challenge Benchmark Suite evaluate various system characteristics, including memory bandwidth, latency, and data access patterns, offering a more holistic understanding of performance.

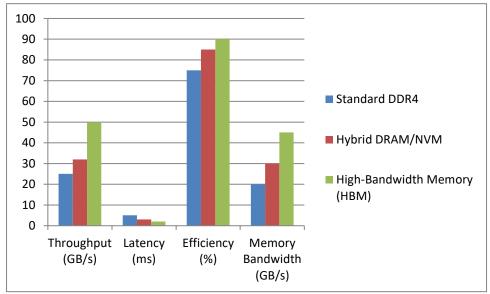

Defining clear performance metrics is fundamental for effective benchmarking. Common metrics include throughput, which measures data processing speed; latency, which indicates the time required for a single operation or data transfer; and efficiency, which reflects how well a system utilizes its resources. These metrics can be tailored to different workloads, ensuring relevant performance assessments. For example, in memory-bound applications, measuring latency and bandwidth is more critical than in compute-bound scenarios. A controlled testing environment is vital for obtaining reliable results. This involves maintaining consistent hardware configurations, software environments, and workloads across tests. Additionally, isolating the benchmarking process from other system activities minimizes external influences that could skew results. Ensuring uniform testing conditions allows researchers to compare performance improvements accurately.

Several case studies highlight the impact of memory optimization strategies on HPC performance. One study using the STREAM benchmark demonstrated that cache blocking improved memory bandwidth utilization by 25% by reducing cache misses and enhancing data locality. Another study on Non-Volatile Memory (NVM) integration showed that hybrid DRAM-NVM architectures reduced execution times by up to 40% for memory-bound applications due to improved data persistence and reduced I/O overhead. A third study on High-Bandwidth Memory (HBM) demonstrated a 1.67x speedup in deep learning training times compared to standard DDR4 configurations, emphasizing HBM's advantage in handling large data volumes efficiently. Performance metrics provide valuable insights into memory optimization effectiveness in HPC systems. Key metrics include throughput, latency, efficiency, and memory bandwidth, each revealing different aspects of system performance. Comparative analysis of various architectures, such as standard DDR4, hybrid DRAM-NVM, and HBM, highlights the benefits of advanced memory technologies. Hybrid architectures improve throughput and latency, while HBM significantly enhances data transfer rates

and overall system efficiency. These findings underscore the importance of adopting memory optimization strategies to enhance performance in HPC environments.

**Table 1. Performance Analysis**

| = 11.00 = 1 = 1 = 1 = 1 = 1 = 1 = 1 = 1 = 1 = |                   |              |                |                            |

|-----------------------------------------------|-------------------|--------------|----------------|----------------------------|

| Architecture                                  | Throughput (GB/s) | Latency (ms) | Efficiency (%) | Memory<br>Bandwidth (GB/s) |

| Standard DDR4                                 | 25                | 5            | 75             | 20                         |

| Hybrid<br>DRAM/NVM                            | 32                | 3            | 85             | 30                         |

| High-Bandwidth<br>Memory (HBM)                | 50                | 2            | 90             | 45                         |

Figure 2. Performance Analysis

#### 5. Challenges and Future Directions

#### 5.1. Scalability Issues in Next-Generation Architectures

As high-performance computing (HPC) systems evolve, scalability emerges as a critical challenge that impacts their performance and efficiency. Scalability refers to the ability of a system to handle increasing workloads by adding resources without compromising performance. The design of next-generation HPC architectures must address several key scalability issues, including hardware integration, software compatibility, and data management.

#### 5.1.1. Hardware Integration

Next-generation HPC architectures often integrate heterogeneous components, such as CPUs, GPUs, and specialized accelerators. While this integration can enhance computational power and parallelism, it also complicates the scalability of the system. Each component may have different performance characteristics and memory access patterns, making it challenging to optimize code for efficient execution across all hardware types. Moreover, the complexity of managing multiple processors and accelerators can lead to increased overhead in workload forecasting and resource allocation, which can hinder overall system scalability.

#### 5.1.2. Software Compatibility

The software stack used in HPC environments must be compatible with the added or removed resources to maintain performance and stability. As new hardware technologies emerge, ensuring that existing software libraries, compilers, and applications can effectively utilize these advancements becomes increasingly difficult. This challenge is exacerbated by the rapid pace of innovation in both hardware and software, requiring constant updates and optimizations to keep systems aligned with current capabilities.

#### 5.1.3. Data Management

Scalability also poses significant challenges in data management. HPC workloads often generate massive volumes of data that need to be processed and stored efficiently. As systems scale up, transferring large datasets between compute nodes and storage systems can become a bottleneck, impacting overall performance. Implementing robust data transfer protocols and storage solutions is essential for managing these large volumes effectively. Additionally, ensuring data integrity and implementing effective backup strategies become increasingly complex as the size of the datasets grows.

#### 5.2. AI and Machine Learning-Driven Memory Optimization

Artificial Intelligence (AI) and machine learning (ML) are transforming various fields, including high-performance computing (HPC), by providing innovative approaches to memory optimization. These technologies enable more intelligent resource management, predictive analytics for workload forecasting, and adaptive memory allocation strategies that enhance overall system performance.

#### 5.2.1. Intelligent Resource Management

AI-driven algorithms can analyze historical usage patterns to optimize memory allocation dynamically. By predicting which data will be accessed frequently based on past behaviors, these algorithms can preemptively allocate memory resources to minimize latency. For instance, machine learning models can learn from application behavior over time to adjust memory configurations automatically based on real-time demands. This proactive approach reduces the need for manual tuning and enhances system responsiveness.

#### 5.2.2. Predictive Analytics for Workload Forecasting

Machine learning techniques can also be employed for workload forecasting in HPC environments. By analyzing historical performance data, AI models can predict future workloads with high accuracy. This capability allows system administrators to allocate resources more effectively and anticipate potential bottlenecks before they impact performance. For example, predictive analytics can inform decisions about scaling up or down based on anticipated demand during peak usage periods.

#### 5.2.3. Adaptive Memory Allocation Strategies

AI and ML facilitate adaptive memory allocation strategies that optimize memory usage based on current workloads. For example, reinforcement learning algorithms can be used to determine the best allocation strategy by continuously evaluating system performance against various configurations. These algorithms learn from ongoing operations and adapt their strategies accordingly to maximize throughput while minimizing latency.

#### 5.3. Potential Research Opportunities

The landscape of high-performance computing (HPC) is rapidly evolving, presenting numerous research opportunities aimed at addressing existing challenges while exploring innovative solutions for future architectures. As technology advances and demands grow across various sectors such as scientific research, artificial intelligence (AI), and big data analytics researchers have the chance to explore several key areas.

#### 5.3.1. Advanced Memory Technologies

One promising research avenue involves investigating advanced memory technologies such as Non-Volatile Memory (NVM), High-Bandwidth Memory (HBM), and Processing-in-Memory (PIM). Researchers can focus on optimizing these technologies for specific applications within HPC environments to enhance performance while reducing latency. Exploring hybrid memory architectures that combine traditional DRAM with emerging technologies could yield significant benefits in terms of speed and efficiency.

#### 5.3.2. AI-Enhanced Resource Management

The integration of AI into resource management systems presents another exciting opportunity. Researchers can develop sophisticated machine learning algorithms that optimize resource allocation dynamically based on real-time workloads or predictive analytics. This area includes exploring reinforcement learning techniques for adaptive scheduling or load balancing in heterogeneous computing environments.

#### 5.3.3. Scalability Solutions

Research focused on developing scalable architectures that accommodate growing computational demands is crucial. This includes designing new interconnect technologies that facilitate low-latency communication between nodes or exploring innovative approaches to data management that streamline access to large datasets across distributed systems.

#### 5.3.4. Energy Efficiency Innovations

As HPC systems become more powerful, energy consumption remains a critical concern. Research opportunities exist in developing energy-efficient architectures that balance performance with sustainability goals. Investigating novel cooling solutions or optimizing power management techniques could contribute significantly to reducing operational costs without sacrificing performance.

#### 6. Conclusion

In conclusion, optimizing memory hierarchy and access strategies is paramount for enhancing the performance of high-performance computing (HPC) architectures. As computational demands continue to escalate across various fields, including scientific research, artificial intelligence, and big data analytics, the importance of efficient memory management becomes increasingly pronounced. This paper has explored a range of optimization strategies, including cache optimization techniques, memory access patterns, and emerging technologies such as Non-Volatile Memory (NVM), High-Bandwidth Memory (HBM), and Processing-in-Memory (PIM). Each of these strategies offers unique advantages that can significantly improve system performance and responsiveness. Moreover, the integration of artificial intelligence and machine learning into memory optimization presents exciting opportunities for future research. By leveraging predictive analytics and adaptive resource management techniques, HPC systems can achieve greater efficiency in handling complex workloads. However, challenges related to scalability, software compatibility, and data management must be addressed to fully realize the potential of next-generation architectures. As researchers continue to explore innovative solutions in these areas, the future of HPC holds promise for even greater advancements in performance, energy efficiency, and overall system capability.

Ultimately, the ongoing evolution of memory technologies and optimization strategies will play a crucial role in shaping the landscape of high-performance computing. By embracing these advancements and addressing existing challenges, researchers and practitioners can ensure that HPC systems remain at the forefront of computational innovation, driving breakthroughs across a wide array of scientific and industrial applications.

#### References

- [1] GeeksforGeeks. (n.d.). *Memory hierarchy design and its characteristics*. Retrieved from https://www.geeksforgeeks.org/memory-hierarchy-design-and-its-characteristics/

- [2] Science.gov. (n.d.). *Memory hierarchy optimization*. Retrieved from https://www.science.gov/topicpages/m/memory+hierarchy+optimization

- [3] Shiksha. (n.d.). *Memory hierarchy in operating system*. Retrieved from https://www.shiksha.com/online-courses/articles/memory-hierarchy-in-operating-system/

- [4] University of Michigan. (n.d.). *Memory hierarchy and optimizations*. Retrieved from https://open.umich.edu/sites/default/files/downloads/col11136-1.5.pdf

- [5] ACM Digital Library. (2022). *Memory hierarchy optimization techniques in HPC*. Retrieved from https://dl.acm.org/doi/fullHtml/10.1145/3570638

- [6] IIT Research Center. (n.d.). *Optimization of memory hierarchy for high-performance computing*. Retrieved from https://grc.iit.edu/research/projects/optmem/

- [7] HAL Theses. (2021). *Advanced memory hierarchy optimizations in modern architectures*. Retrieved from https://theses.hal.science/tel-03836248v1/file/100950\_SEZNEC\_2021\_archivage.pdf

- [8] GeeksforGeeks. (n.d.). *Basic cache optimization techniques*. Retrieved from https://www.geeksforgeeks.org/basic-cache-optimization-techniques/

- [9] University of Crete. (n.d.). *Advanced memory hierarchy and cache optimizations*. Retrieved from https://www.csd.uoc.gr/~hy460/pdf/AMH/10.pdf

- [10] MDPI Electronics. (2023). *Data locality in high-performance computing and big data systems: An analysis*. Retrieved from https://www.mdpi.com/2079-9292/12/1/53

- [11] ResearchGate. (2023). Data locality in HPC and converged systems. Retrieved from https://www.researchgate.net/publication/365262894\_Data\_Locality\_in\_High\_Performance\_Computing\_Big\_Data\_and\_Converged\_Systems\_An\_Analysis\_of\_the\_Cutting\_Edge\_and\_A\_Future\_System\_Architecture

- [12] IEEE Xplore. (2008). *Data locality and memory optimization techniques in computing systems*. Retrieved from https://ieeexplore.ieee.org/document/4637712/

- [13] NTT Review. (2017). *High-speed memory access and latency reduction techniques*. Retrieved from https://www.ntt-review.jp/archive/ntttechnical.php?contents=ntr201704ra1.html

- [14] IBM. (n.d.). High-performance computing: Topics and trends. Retrieved from https://www.ibm.com/think/topics/hpc

- [15] AWS Documentation. (n.d.). *Networking in high-performance computing*. Retrieved from https://docs.aws.amazon.com/es\_es/wellarchitected/latest/high-performance-computing-lens/networking.html

- [16] ResearchGate. (2023). Latency reduction techniques in high-speed data networks. Retrieved from https://www.researchgate.net/publication/375112271\_Latency\_reduction\_techniques\_in\_high\_speed\_data\_networks

- [17] OSTI. (2018). *Non-volatile memory systems and architectures for HPC*. Retrieved from https://www.osti.gov/servlets/purl/1457932

- [18] IEEE Xplore. (2017). *Emerging trends in non-volatile memory technologies*. Retrieved from https://ieeexplore.ieee.org/document/8026869/

- [19] Renesas. (n.d.). *Non-volatile memory solutions*. Retrieved from https://www.renesas.com/en/products/memory-logic/non-volatile-memory

- [20] Admin Magazine. (n.d.). Finding memory bottlenecks with Stream benchmarks. Retrieved from https://www.admin-magazine.com/HPC/Articles/Finding-Memory-Bottlenecks-with-Stream

- [21] HPC-Wiki. (n.d.). Micro benchmarking in HPC systems. Retrieved from https://hpc-wiki.info/hpc/Micro\_benchmarking

- [22] IEEE Xplore. (2014). Benchmarking of HPC systems: Challenges and solutions. Retrieved from https://ieeexplore.ieee.org/document/6903790/

- [23] ArXiv. (2024). Challenges in high-performance computing architectures. Retrieved from http://arxiv.org/pdf/2408.10281.pdf

- [24] Penguin Solutions. (n.d.). *Overcoming platform complexity in HPC systems*. Retrieved from https://www.penguinsolutions.com/company/resources/newsroom/hpc-challenges-overcoming-platform-complexity

- [25] PhoenixNAP. (n.d.). HPC architecture and trends in modern computing. Retrieved from https://phoenixnap.com/kb/hpc-architecture

- [26] Intel. (n.d.). *High-performance computing architecture*. Retrieved from https://www.intel.com/content/www/us/en/high-performance-computing/hpc-architecture.html

- [27] HPC Wire. (2022). Accelerating the development of next-generation HPC and AI system architectures. Retrieved from https://www.hpcwire.com/2022/05/09/accelerating-the-development-of-next-generation-hpc-ai-system-architectures-with-ucie-compliant-optical-i-o/