#### International Journal of Emerging Trends in Computer Science and Information Technology

ISSN: 3050-9246 | https://doi.org/10.63282/3050-9246/IJETCSIT-V6I1P107 Eureka Vision Publication | Volume 6 Issue 1 PP 56-63, 2025

Original Article

# Emerging Advanced Packaging Technologies and Their Impact on Modern Computer Architecture

Shivakumar Udkar

Senior Manager Design Engineering AMD Inc., Colorado, USA.

Received On: 20/01/2025 Revised On: 03/02/2025 Accepted On: 16/02/2025 Published On: 05/03/2025

Abstract - Modern computer architecture is heavily dependent on advanced packaging technologies. As Moore's Law begins to decline, semiconductor manufacturers will continue performance scaling by means of innovations in packaging. However, technologies to implement 2.5D, 3D integration, Fan-Out Wafer Level Packaging (FOWLP), and chiplet architecture all contain distinct performance, power efficiency, and integra—tion density advantages. This paper analytically studies the methodologies of emerging advanced packaging technologies and their impact on modern computing paradigms. This paper presents a comparative study that illustrates how these technologies can reduce the form factor and consume less power while improving computing performance. Key applications, namely data centers, HPC, and Edge Computing, are discussed. We finally discuss the current challenges, what the prospects might be, and what may be the potential breakthroughs to advanced semiconductor packaging.

**Keywords** - Advanced Packaging, Chiplet Architecture, 3D Integration, Fan-Out Wafer-Level Packaging (FOWLP), Modern Computing.

#### 1. Introduction

### 1.1. Evolution of Semiconductor Packaging

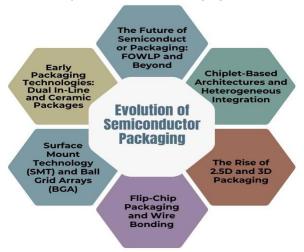

Figure 1. Evolution of Semiconductor Packaging

Early Packaging Technologies: Dual In-Line and Ceramic Packages: Initial semiconductor packaging was in the form of Dual In-Line Packages (DIP) and Ceramic Packages that were able to protect and Connect Integrated Circuits (ICs). The only purposes for which these packages were used were on early computing and electronic devices, and they had small pin counts. [1-3] With increased processing requirements, chip complexity increased, and more complex packaging techniques were required.

- Surface Mount Technology (SMT) and Ball Grid Arrays (BGA): Surface Mount Technology (SMT) introduced arguably the most significant change to the semiconductor packaging: it allowed for smaller and more cramped layouts. A technology that evolved and was of vital importance was the Ball Grid Array (BGA) package, which left the traditional lead packages and substituted this option by laying the chip's bottom with a surface with solder balls. BGA was a standard for high-performance processors as a result of this innovation, which greatly improved electrical and thermal dissipation and mechanical reliability.

- Flip-Chip Packaging and Wire Bonding: In IC packaging, traditional wire bonding was carried out widely, and it was a bottleneck as chip speeds increased with longer interconnect lengths. The solution to this problem was flip chip packaging, whereby the chip is directly mounted to the substrate, drastically reducing interconnect distances and improving signal integrity. As high-speed processors and GPUs gained in popularity, a technology called a flip chip, which worked in communicating and thermal management, came into its own.

- The Rise of 2.5D and 3D Packaging: With the ongoing miniaturization of the device, 2.5D and 3D packaging technologies were developed to interconnect limitations such as 2.5D uses an interposer to tie many dies in concert, improving

bandwidth and power utilization, 3D stacking, which stacks dies on top of each other using Through Silicon Vias (TSVs) to better reduce latency and power. Widespread in High-Performance Computing (HPC), Artificial Intelligence (AI), and data centers, they are widely used.

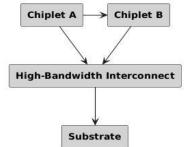

- Chiplet-Based Architectures and Heterogeneous Integration: During the past years, as the cost and complexity in monolithically SoC design rise, the chipset-based design has become popular, as manufacturers now generate several chipsets and combine them within the same package to turn into a complete system. The heterogeneous integration combines different technologies (CPU, GPU, AI accelerators, memory) with this integration approach; therefore, scalability, cost reduction, and flexibility can be achieved.

- The Future of Semiconductor Packaging: FOWLP and Beyond: Recently, Fan-Out Wafer Level Packaging (FOWLP) led to an attractive new electronic packaging with the removal of traditional substrates for densifying interconnects and promoting better thermal performance. To take further semiconductor devices' performance, future research in 3D heterogeneous integration, advanced cooling techniques, and new radials are working. In this era of Moore's Law nearing a halt, the packaging will be the key to the innovations in how the computing architectures of the next generation will come about.

# 1.2. The Role of Advanced Packaging in Computer Architecture

Due to the physical limitations of Moore's Law, advanced packaging technologies have become an equally important enabler of next-generation computing architectures. Component integration limits, namely power efficiency and heat dissipation, as well as interconnect challenges, hinder the use of traditional monolithic designs, wherein all components are packaged on a single die. On the other hand, techniques of advanced packaging, including 2.5D integration, 3D stacking, chipset-based architectures, and Fan-Out Wafer Level Packaging (FOWLP), represent innovative solutions for increasing the system performance, increasing scaling, and decreasing the power consumption. [4,5] One of the most attractive features of advanced packaging is its capability to improve density and also to reduce the latency of signals by increasing components' closeness. For instance, 2.5D packaging employs an interposer to attach multiple dies for enhanced bandwidth without compromising design flexibility, and 3D stacking vertically integrates many dies using Through Silicon Via (TSV) with a distance of interconnects miniaturized to a great extent and improves energy efficiency. However, 3D stacking is accompanied by thermal critiques, for which new cooling solutions are needed to attenuate heat accumulation. The next revolution in computing comes in the form of chiplet-based architectures, where complex System-On-Chip (SoC) designs are broken down into smaller, reusable chiplets for modular integration and cost-effective manufacturing. By employing this approach, designers can intermix different chiplets to experiment with a performance at the expense of power consumption, based on the workload they're powering, either for HPC, AI accelerators, or edge devices. FOWLP technology also increases electrical and thermal performance, reduces bulkiness, and increases the degree of integration in a small form factor. Overall, advanced packaging is a vital element in modern computer architecture for overcoming scaling limits and enabling further performance, power efficiency, and integration. Heterogeneous integration via advanced packaging will continue to be the basis for future processor innovation in AI, cloud computing, and mobile devices as computing demands rise.

# 1.3. The Impact of Moore's Law and the Need for Advanced Packaging

Moore's Law was that the number of transistors on a chip would double every two years or so, and it has been a driving force behind the speed of semiconductor technology. Exponential improvements in processing power, energy efficiency, miniaturization, and cost figures are a result of this trend. But as transistor sizes shrink to the limits of atomic-scale physics, the type of performance improvements that entail and that derive from transistor scaling have become increasingly difficult and expensive to achieve. Power density, heat dissipation, and fabrication costs have tied the hands of manufacturers, restricting them from shriving transistors at the same pace, and this has often been called the slowdown of Moore's law.

Hence, the semiconductor industry has moved out of scaling transistors to advanced packaging technologies as a means to attain performance gains. For continued improvements, advanced packaging enhances chip interconnectivity, reduces power consumption, and increases data transfer speeds without depending entirely, for instance, on the miniaturization of transistors. Therefore, techniques, including 2.5D and 3D integration, chiplet based architectures, FOWLP, and others, have emerged as key solutions to maintain the projected trajectory of computational development.

Because of these advantages, 2.5D packaging uses an interposer to package multiple dies, higher interconnect bandwidth, and lower latency than traditional PCB-based interconnects, while 3D stacking stacks multiple dies vertically at TSVs for performance and reduced footprint of semiconductor devices. Nevertheless, these issues of heat dissipation and manufacturing complexity still need to be overcome before widespread adoption. Chiplet-based design is another major innovation, where it directly scales out of a monolithic SoC to integrate smaller, modular chiplets onto a single package. The approach enhances scalability and yields and promotes heterogeneous integration by enabling the integration of many basic and component class chips for the processor to leverage the combination of specialized processors, including those optimized for AI, machine learning, and cloud computing workloads. Like FOWLP,

FOWLP re-distributes interconnects at the wafer level, so no traditional substrates are required, which improves both thermal efficiency and electrical performance.

In this Moore's Law world of slowing, however, advanced packaging is becoming the key enabler for next-generation semiconductor technology. Using novel packaging techniques, the industry can sustain the drive for stronger performance, power efficiency, and miniaturization and avoid limiting computing power growth in an age in which transistor scaling alone is insufficient. Future work will examine cost-effective manufacturing, reduced thermal issues, and novel materials to reduce costs further, improve thermal performance, and move to a commercial scale.

# 2. Literature Survey

## 2.1. Traditional vs. Advanced Packaging Techniques

#### 2.2.1 2.5D Integration

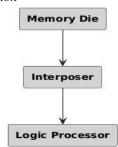

Figure 2. 2.5D Integration

latency is high. Heterogeneous integration using different dies (logic processors, memory, and AI accelerators) on the same interposer is also possible. This approach has wide acceptance in HPC, GPUs, and AI-driven applications because it makes the designs more flexible and power-efficient. However, there are still other areas, like the cost of interposer and high manufacturing complexity, under active research.

#### 2.2.2. 3D Stacking

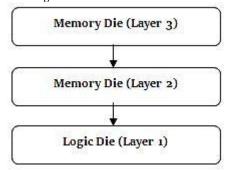

Figure 3: 3D Stacking

The technique of 3D stacking vertically integrates multiple dies using Through Silicon Vias (TSVs), tiny vertical electrical connections to pass through silicon wafers. This method significantly reduces signal latency and bandwidth utilization due to shorter signal path distances than conventional 2D interconnects, and it leads to a smaller

The traditional semiconductor packaging methods take proper care of basic die protection and electrical connections through wire bonding or flip-chip techniques. As is generally the case, these methods have low interconnect density, moderate power efficiency, and poor thermal dissipation capabilities. [6-9] Homogeneous integration has been their main theme and the components are essentially fabricated using the same process technologies.

On the other hand, advanced packaging techniques are aimed to enhance performance, power efficiency, and integration flexibility. These provide higher interconnect density as well as better thermal dissipation through innovative 2.5D and 3D stacking approaches. In addition, embroidered packaging facilitates heterogeneous integration by allowing various chip types (logic, memory, and analog) to be combined to enhance performance in a single package.

#### 2.2. Key Developments in Advanced Packaging

footprint of the device, which makes it an ideal candidate for high-speed memory modules, FPGAs, and AI accelerators. The main obstacle to 3D stacking, however, is the fact that when increasing the number of dies to multiple, the die area results in increasing power density and, consequently, heat generation, which can be problematic for performance. The application of 3D integration puts forward challenges for cooling, and researchers are actively exploring advanced cooling techniques, like microfluidic cooling and thermal-aware design strategies, to address these challenges and unlock the full potential of 3D integration.

# 2.2.3. Chiplet-Based Design

Figure 4. Chiplet-Based Design

2.2.4. Fan-Out Wafer-Level Packaging (FOWLP)

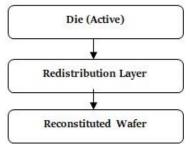

Figure 5. Fan-Out Wafer-Level Packaging

As compared to an interposer, the electrical performance, integration density, and thermal efficiency have all been improved using Fan-Out Wafer-Level Packaging (FOWLP). Unlike conventional packaging methods, which use substrates, FOWLP transfers I/O connections off a reconstituted wafer, resulting in a more compact design with better heat dissipation. Thus, this technology eliminates parasitic losses, improves signal integrity, and enables high gradient density integration, all of which are particularly advantageous for mobile processors, HPC, and automotive applications. The FOWLP has a smaller form factor and lower resistance than traditional wire bonding and flip-chip packaging, which can be achieved at a lower cost. Since power efficiency and performance are critical in smartphones and AI accelerators, they have been widely adopted. Given the evolution of FOWLP, additional developments in multi-layer fan-out packaging will be expected to extend its adoption in high-performance computing environments.

#### 2.3 Research Trends and Gaps

Continued advancements in advanced packaging technologies remain hampered by several challenges. However, thermal management is still an important issue, particularly in 3D stack and high-power applications in which heat dissipation efficiency has to be improved. Furthermore, reliability can be addressed through the selection of material, as issues such as warpage, electromigration, and mechanical stress need to be addressed. The latter is reflected in their concern for cost efficiency: advanced packaging processes can involve higher

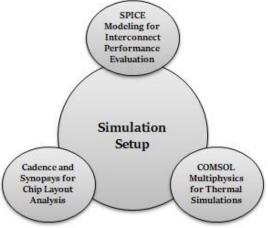

Figure 6. Simulation Setup

• Cadence and Synopsys for Chip Layout Analysis: The physical layout of the

fabrication and assembly expenses. In particular, this paper explores these two challenges in detail and then proposes ideas that will help improve the efficiency and practicability of advanced packaging techniques.

# 3. Methodology

#### 3.1. Comparative Analysis Framework

A structured comparative analysis framework was developed to enable a systematic packaging evaluation among various types of technologies. Power consumption of the photodetector and the overall system are explored as a function of their key performance indicators (such as integration complexity). The static and dynamic power consumption is estimated, and it is believed that advanced packaging techniques will be directed towards reducing power leakage to decrease overall power consumption through better energy efficiency. [10-13] Yet computing efficiency and reliability depend on parameters such as interconnect density, data transfer rate, and thermal dissipation capacity, which are all directly related to performance and, as such, are accounted for in evaluating the performance. The ease of integration within several dies, the feasibility of heterogeneous integration, and manufacturing challenges for each packaging approach are discussed to perform the integration complexity analysis. This framework is applied to allow the selection of one of the packaging technologies based on the objectification of diverse packaging technologies and the most suitable to specific application needs.

# 3.2. Simulation Setup

A comprehensive simulation framework was developed to rigorously assess the performance of different packaging approaches under real-world computing workloads. Within this framework, multiple industry standard tools are integrated to analyze critical fashion, such as chip layout and delivery, tight performance, and interconnect habit. The study does this by using these simulations to create a detailed evaluation of how other packaging techniques can alter the final overall system performance and reliability.

semiconductor package has been designed and analyzed using Cadence and Synopsys tools. This provides an ability to analyze interconnect density, routing complexity, and overall area efficiency. Different packaging configurations were simulated, and insights on design trade-offs, including signal integrity, power distribution, and manufacturability, were acquired.

• COMSOL Multiphysics for Thermal Simulations: This is critical, especially in 3D stacked designs, as in advanced packaging, thermal management plays a critical role. Heat dissipation patterns, thermal gradients, and hot spots were modeled, and thermal gradients were evaluated using COMSOL Multiphysics. By running these simulations, one can optimize cooling strategies and material selection to increase reliability and performance under high power workloads.

**SPICE Modeling for Interconnect Performance** SPICE **Evaluation:** was used to model interconnects and assess the electrical performance of interconnects within different packaging approaches. Detailed signal integrity, propagation delay, and power loss were provided by SPICE simulations on interconnects. Using circuit simulation to analyze the impact this has on the overall performance of the circuit was crucial to determining how packaging choices affect total performance, especially in high-speed computing applications.

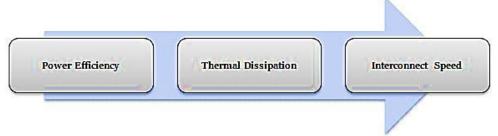

#### 3.3. Performance Metrics

• Power Efficiency: There is believed to be powerefficient semiconductor packaging when the

performance should be high, but the energy

consumption must be reduced. It further reduces

the interconnect length from resistive losses

through advanced packaging such as 3D stacking

and chiplet-based designs. In addition, interposers

are designed to lower power consumption in total,

and Power Delivery Networks (PDNs) are also

used to decrease power consumption. Battery

packaging solutions for mobile devices and highperformance computers will optimize battery life,

as well as reduce operation costs and heat

generation.

Figure 7. Performance Metrics

- Thermal Dissipation: Effective thermal dissipation is needed for the reliable and long life of semiconductor devices. When the density of the package in 3D stacked architecture is increased, it becomes more challenging to manage heat. Active cooling with thermal vias and high conductivity is used to reduce the heat and boost heat dissipation. These are simulation tools, namely COMSOL Multiphysics, that are used to simulate modeling heat flow and thermal management strategy optimization. Thermal dissipation improvement helps prevent performance degradation, achieve thermal stress, and improve the system's overall stability.

- Interconnect Speed: Interconnect speed directly determines the system performance and data transmission rates. However, inherently bandwidth and higher latency limited by wire bonding methods, high-density RDLs, and TSVs already have much higher inter-connect speed compared to wire bonding methods, which, together with 2.5D and 3D integration technologies, shorten interconnect distance and thus reduce signal propagation delay and increase data transfer efficiency. In applications of artificial intelligence, data centers, and high-performance computing, latency, and bandwidth-heavy are necessary.

#### 3.4. Flowchart semiconductor packaging

• **Start:** The process starts with defining the objectives and narrows the scope of the study. The

- first phase would be to identify key semiconductor packaging challenges such as power efficiency, thermal dissipation, and interconnect performance. With a clear research focus, the comparative analysis allows the industry to address needs that are pertinent to the industry. [14-16] The study defines well-described goals but gives practical insights into the tradeoffs in different packaging techniques.

- **Define Metrics:** The Key Performance Metrics (KPMs) are defined to ensure a standardized comparison. Among these are power consumption, interconnect density, thermal resistance, signal integrity, and integration complexity as a whole. These metrics help establish the measure of objective evaluation of each packaging technology. Depending on the applied area, whether mobile devices, high-performance computing, or data centers, one chooses the metrics to apply.

- Select Technologies: Industry trends and technological advancements determine the selection of a range of semiconductor packaging technologies. Traditionally, such selection typically includes conventional packaging methods as well as advanced packaging techniques, including 2.5D integration, 3D stacking, and Fan Out Wafer Level packaging (FOWLP). The technologies should be relevant to present and future semiconductor design requirements to guarantee that the study applies to real-world applications.

- Conduct Simulations: Selected packaging technologies are evaluated by means of simulations

using industry-standard tools. The thermal performances are simulated with COMSOL Multiphysics, chip layout analyses are performed with Cadence and Synopsys tools, and SPICE is used to analyze interconnect analyses. This work quantifies the effect of various packaging options on the power efficiency, thermal power dissipation, and signal integrity sense. Real-world computing workloads are used to validate performance in different scenarios.

• Analyze Results: The packaging techniques were then simulated until all the data could be analyzed and trends, strengths, and weaknesses identified. It compares performance, power consumption, temperature distribution, and interconnect speed to identify which technology offers the best tradeoff between performance, power, and complexity of integration. The insights proved to be critically important when considering how to trade off and what opportunities for further design of the package might exist.

Figure 8. Flowchart semiconductor packaging

### 4. Results and Discussion

#### 4.1. Performance Evaluation

Advanced packaging simulations show clearly that advanced packaging technology solutions allow significant improvements in system performance with power efficiency improvement, reduction in latency, and increased interconnect bandwidth. Traditional packaging approaches that require longer interconnects, as well as conventional power networks,s tend to consume higher power and delay the signals. Unlike advanced techniques like 2.5D integration and 3D stacking, they make use of different interconnect architectures that limit power dissipation and enhance data transfer speeds. In 2.5D packaging, high bandwidth communication between multiple dies is introduced, which leads to a reduction in the need for power-hungry long-range connections and overall efficiency. Similar to 3D stacking, TSV-based vertical integration of multiple dies increases power savings by reducing interconnect paths vertically, which lowers resistance. By virtue of this vertical integration, it reduces energy consumption and also improves signal integrity, which makes it a particularly good fit for high-performance applications like Artificial Intelligence (AI) and cloud computing. However, while this increased power density could provide significant performance gains, it imposes a high thermal challenge since overheating can limit any gains. Chiplet-based architectures increase the modularity of architecture by utilizing smaller, pre-tested functional blocks (chiplets) that are integrated within a single package. It gives better modularity, better design flexibility, scalability, and lower development costs than monolithic system-on-chip (SoC). Furthermore, chiplets provide better power distribution because power domains can be controlled finer, meaning that active components consume power and idle areas remain in low power states.

On the whole, advanced packagings technologies provide a great gain in performance efficiency as loss of power, signal latency, and interconnect bandwidth are minimized. Due to these advancements, these are especially well suited for next-generation computing workloads like High-Performance Computing (HPC), edge AI, and mobile processors that are blindingly fast and also efficient.

#### 4.2. Impact on Thermal Dissipation

Due to poor performance, low reliability, and short-circuiting of electronic devices, semiconductor packaging involves thermal management as a critical factor, as high heat can cause it. However, even though it is, thermal simulations indicate that advanced packaging technologies yield superior heat dissipation compared to traditional monolithic chips. These include chiplet-based and Fan-Out Wafer Level Packaging (FOWLP) as more efficient solutions for efficient thermal performance.

Thanks to how their distribution architecture spreads heat around the package, the localized hotspots are reduced, and heat spread becomes even around the package. The architecture of the chiplet enabled thermal management to gain more performance using multiple smaller dies placed in a single package than would be the case with a single larger die. Honouring that power density can be reduced with optimally placed heat-producing components, power density per known unit area is reduced, and better thermal management is made possible.

Ultimately, chiplets can also be designed with independent power domains such that any surplus, unnecessary heat generation would only be conducted on areas in the system actively using power. The technology it utilizes has a similar fan-out redistribution layer used for spreading the heat more efficiently and does away with the need for an interposer for additional heat dissipation, like FOWLP. Of special significance for this last point is the fact that FOWLP is free of the bulky substrate and has direct contact of dies with the redistribution layer, both of which enhance heat conduction and are a good choice for high-performance mobile applications where cooling is a critical matter.

On the other hand, 3D stacking provides a substantial reduction in interconnect bandwidth and latency through vertical stacking of dies, but at the same time, it introduces thermal issues because of vertically stacking multiple dies. Nevertheless, with increasing power density in 3D stacked architectures, the heat buildup increases, and more advanced cooling solutions are needed, such as Through-Silicon Vias (TSVs) with a thermal path built-in, microfluidic cooling, and enhanced heat spreaders.

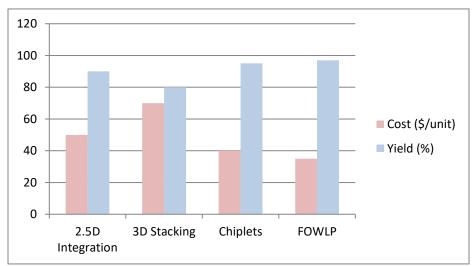

Table 1: Cost and Yield Analysis of Advanced Packaging

| 1 centiologies   |                |           |

|------------------|----------------|-----------|

| Technology       | Cost (\$/unit) | Yield (%) |

| 2.5D Integration | 50             | 90        |

| 3D Stacking      | 70             | 80        |

| Chiplets         | 40             | 95        |

| FOWLP            | 35             | 97        |

## 4.3. Economic and Manufacturing Considerations

Though advanced package technologies provide significant performance and thermal management advances, economic feasibility imposes a key constraint on their large-scale adoption. The practicality of each of the packaging approaches depends on the manufacturing yield and the cost per unit.

Defective units can be replaced without having to throw out the entire system since chiplets are modular. Fan-Out Wafer Level Packaging (FOWLP) is the least expensive, with a unit cost of \$35 per unit and a maximum yield of 97%. FOWLP eliminates the need for an interposer by virtue of eliminating an interposer and still offers excellent electrical and thermal performance. They achieve a high yield due to their streamlined manufacturing process, lacking the challenges of TSV and the complex bonding step.

Figure 9. Graph representing Cost and Yield Analysis of Advanced Packaging Technologies

## 5. Conclusion

#### 5.1. Summary of Findings

Semiconductor packaging has become a critical enabler in the evolution of next-generation computing performance. Advanced packaging technologies such as 2.5D integration, 3D stacking, chiplet-based architectures, and Fan-Out Wafer-Level Packaging (FOWLP) offer significant improvements in power efficiency, interconnect density, and thermal management compared to traditional monolithic designs. 2.5D integration, which employs an interposer for die-to-die communication, enhances bandwidth and reduces latency.

3D stacking further interconnects lengths by vertically integrating multiple dies using through-silicon vias (TSVs), leading to improved power efficiency and performance but also posing thermal management challenges. On the other hand, a scalable and cost-efficient approach is offered by chiplet-based designs that integrate several smaller independently manufactured dies within

respective packages to reduce the overall design complexity and manufacturability. FOWLP finally enables excellent electrical performance without interposers, with manufacturing yield, and with cost-effectiveness. Each of these packaging solutions has a role in the future of high-performance computing, AI accelerators, and mobile processors.

#### 5.2. Future Research Directions

These advances notwithstanding, a number of challenges remain, and more research and development is needed. The high-performance characteristic is one of the main areas of focus, although efforts are also being made to develop cost-effective and 3D packaging methods that can provide high yields. However, 3D stacking currently comes at a high price since fabrication steps and losses in yield are possible if any of the stacked layers are defective.

Since increased power densities in 3D stacked architectures generate excessive heat buildup, the thermal management solutions also need to be improved. To ensure

long-term viability, research needs to be done on innovative cooling strategies such as embedded microfluidic cooling, innovative heat spreaders, and advanced thermally conductive materials. The interconnects also need to have new materials for interconnects to be able to improve signal integrity and decrease power losses.

However, traditional copper interconnects are approaching their performance limits, and alternative interconnects like graphene-based interconnects, optical interposers, and carbon nanotubes are thought to have superior electrical and thermal properties for the next-generation packaging solutions.

#### 5.3. Final Thoughts

Traditionally, scaling transistors down smaller and smaller is how the semiconductor industry moves forward, but now that the semiconductor industry is moving beyond Moore's Law, increasing the number of transistors doesn't keep up with the need for increases in computing performance. Future innovations, however, will be driven by heterogeneous integration and advanced packaging techniques. As researchers and manufacturers continue to work and develop more efficient, scalable, and cost-effective solutions for chiplet-based architectures, 3D stacked processors can be witnessed to move forward with high-density interconnect technologies.

However, for widespread adoption, manufacturing costs must be addressed, material selection must be made, and thermal regulation must be provided. To advance packaging technology, future work will require collaboration between the material sciences and electrical engineering with semiconductor manufacturers. The next era of computing will be based on R&D investments that enable advances in fabrication techniques and cooling mechanisms, resulting in the development and integration of advanced packaging into high-performance, energy-efficient semiconductor systems.

### References

- [1] Pavlidis, V. F., Savidis, I., & Friedman, E. G. (2017). Three-dimensional integrated circuit design. Newnes.

- [2] Xie, Y., Cong, J., & Sapatnekar, S. (2010). Threedimensional integrated circuit design. EDA, Des. Microarchitectures, 20, 194-196.

- [3] Topol, A. W., La Tulipe, D. C., Shi, L., Frank, D. J., Bernstein, K., Steen, S. E., ... & Ieong, M. (2006). Three-dimensional integrated circuits. IBM Journal of Research and Development, 50(4.5), 491-506.

- [4] Lu, D., & Wong, C. P. (Eds.). (2009). Materials for advanced packaging (Vol. 181). Boston, MA, USA: Springer US.

- [5] Hennessy, J. L., & Jouppi, N. P. (1991). Computer technology and architecture: An evolving interaction. Computer, 24(9), 18-29.

- [6] Chen, Z., Zhang, J., Wang, S., & Wong, C. P. (2023). Challenges and prospects for advanced packaging. Fundamental Research.

- [7] Cao, L., & Krusius, J. (1995). Concurrent packaging architecture design. IEEE Transactions on Components,

- Packaging, and Manufacturing Technology: Part B, 18(1), 66-73.

- [8] Yuan, Y. (2024, July). 3D packaging and Moore's Law. In Journal of Physics: Conference Series (Vol. 2798, No. 1, p. 012048). IOP Publishing.

- [9] Next-Gen Electronics: Exploring the Impact of Advanced Semiconductor Packaging, electronics era, online. https://electronicsera.in/next-gen-electronicsexploring-the-impact-of-advanced-semiconductorpackaging/

- [10] Iyer, S. S. (2017, October). Packaging without the Package is More Holistic than Moore's Law. In International Symposium on Microelectronics (Vol. 2017, No. S1, pp. 1-40). International Microelectronics Assembly and Packaging Society.

- [11] Khalid, S., Hassan, S. A., Javaid, H., Zahid, M., Naeem, M., Bhat, Z. F., ... & Aadil, R. M. (2024). Factors responsible for spoilage, drawbacks of conventional packaging, and advanced packaging systems for tomatoes. Journal of Agriculture and Food Research, 15, 100962.

- [12] Mahalik, N. P. (2014). Advances in packaging methods, processes, and systems. Challenges, 5(2), 374-389.

- [13] Wang, H., Ma, J., Yang, Y., Gong, M., & Wang, Q. (2023). A review of system-in-package technologies: application and reliability of advanced packaging. Micromachines, 14(6), 1149.

- [14] Advanced Packaging Design Processes for Modern Technology Challenges, Zuken, online. https://www.zuken.com/us/blog/advanced-packaging-design-processes-for-modern-technology-challenges/

- [15] Mallik, D., Radhakrishnan, K., He, J., Chiu, C. P., Kamgaing, T., Searls, D., & Jackson, J. D. (2005). Advanced Package Technologies for High-Performance Systems. Intel Technology Journal, 9(4).

- [16] Witek-Krowiak, A., Szopa, D., & Anwajler, B. (2024). Advanced Packaging Techniques—A Mini-Review of 3D Printing Potential. Materials, 17(12), 2997.

- [17] Beica, R., Ivankovic, A., Buisson, T., Kumar, S., & Azemar, J. (2015, October). The growth of advanced packaging: An overview of the latest technology developments, applications, and market trends. In International Symposium on Microelectronics (Vol. 2015, No. 1, pp. 000001-000005). International Microelectronics Assembly and Packaging Society.

- [18] Understanding Advanced Packaging Technologies and Their Impact on the Next Generation of Electronics, Semiconductor Engineering, online. https://semiengineering.com/understanding-advanced-packaging-technologies-and-their-impact-on-the-next-generation-of-electronics/

- [19] Udkar S. Harnessing Photonic Computing for Next-Generation CPUs and GPUs in High-Performance Computing. 2022, 5(4):23-36.

- [20] Cabrera-Rios, M., Mount-Campbell, C. A., & Irani, S. A. (2002). An approach to the design of a manufacturing cell under economic considerations. International Journal of Production Economics, 78(3), 223-237.